|

Da Vinci Firmware 1

Firmware for the DaVinci-M rocket avionics board.

|

|

Da Vinci Firmware 1

Firmware for the DaVinci-M rocket avionics board.

|

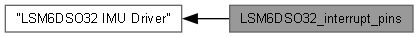

This section groups all the functions that manage interrupt pins. More...

Functions | |

| int32_t | lsm6dso32_int1_mode_set (stmdev_ctx_t *ctx, lsm6dso32_int1_pd_en_t val) |

| Connect/Disconnect INT1 internal pull-down.[set]. | |

| int32_t | lsm6dso32_int1_mode_get (stmdev_ctx_t *ctx, lsm6dso32_int1_pd_en_t *val) |

| Connect/Disconnect INT1 internal pull-down.[get]. | |

| int32_t | lsm6dso32_pin_int1_route_set (stmdev_ctx_t *ctx, lsm6dso32_pin_int1_route_t *val) |

| Select the signal that need to route on int1 pad.[set]. | |

| int32_t | lsm6dso32_pin_int1_route_get (stmdev_ctx_t *ctx, lsm6dso32_pin_int1_route_t *val) |

| Select the signal that need to route on int1 pad.[get]. | |

| int32_t | lsm6dso32_pin_int2_route_set (stmdev_ctx_t *ctx, lsm6dso32_pin_int2_route_t *val) |

| Select the signal that need to route on int2 pad.[set]. | |

| int32_t | lsm6dso32_pin_int2_route_get (stmdev_ctx_t *ctx, lsm6dso32_pin_int2_route_t *val) |

| Select the signal that need to route on int2 pad.[get]. | |

| int32_t | lsm6dso32_pin_mode_set (stmdev_ctx_t *ctx, lsm6dso32_pp_od_t val) |

| Push-pull/open drain selection on interrupt pads.[set]. | |

| int32_t | lsm6dso32_pin_mode_get (stmdev_ctx_t *ctx, lsm6dso32_pp_od_t *val) |

| Push-pull/open drain selection on interrupt pads.[get]. | |

| int32_t | lsm6dso32_pin_polarity_set (stmdev_ctx_t *ctx, lsm6dso32_h_lactive_t val) |

| Interrupt active-high/low.[set]. | |

| int32_t | lsm6dso32_pin_polarity_get (stmdev_ctx_t *ctx, lsm6dso32_h_lactive_t *val) |

| Interrupt active-high/low.[get]. | |

| int32_t | lsm6dso32_all_on_int1_set (stmdev_ctx_t *ctx, uint8_t val) |

| All interrupt signals become available on INT1 pin.[set]. | |

| int32_t | lsm6dso32_all_on_int1_get (stmdev_ctx_t *ctx, uint8_t *val) |

| All interrupt signals become available on INT1 pin.[get]. | |

| int32_t | lsm6dso32_int_notification_set (stmdev_ctx_t *ctx, lsm6dso32_lir_t val) |

| Interrupt notification mode.[set]. | |

| int32_t | lsm6dso32_int_notification_get (stmdev_ctx_t *ctx, lsm6dso32_lir_t *val) |

| Interrupt notification mode.[get]. | |

This section groups all the functions that manage interrupt pins.

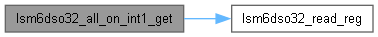

| int32_t lsm6dso32_all_on_int1_get | ( | stmdev_ctx_t * | ctx, |

| uint8_t * | val | ||

| ) |

All interrupt signals become available on INT1 pin.[get].

| ctx | read / write interface definitions |

| val | change the values of int2_on_int1 in reg CTRL4_C |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3638 of file lsm6dso32_reg.c.

References lsm6dso32_ctrl4_c_t::int2_on_int1, LSM6DSO32_CTRL4_C, and lsm6dso32_read_reg().

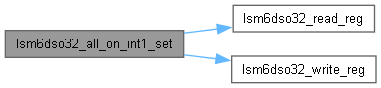

| int32_t lsm6dso32_all_on_int1_set | ( | stmdev_ctx_t * | ctx, |

| uint8_t | val | ||

| ) |

All interrupt signals become available on INT1 pin.[set].

| ctx | read / write interface definitions |

| val | change the values of int2_on_int1 in reg CTRL4_C |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3614 of file lsm6dso32_reg.c.

References lsm6dso32_ctrl4_c_t::int2_on_int1, LSM6DSO32_CTRL4_C, lsm6dso32_read_reg(), and lsm6dso32_write_reg().

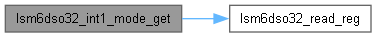

| int32_t lsm6dso32_int1_mode_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_int1_pd_en_t * | val | ||

| ) |

Connect/Disconnect INT1 internal pull-down.[get].

| ctx | read / write interface definitions |

| val | Get the values of pd_dis_int1 in reg I3C_BUS_AVB |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3077 of file lsm6dso32_reg.c.

References LSM6DSO32_I3C_BUS_AVB, LSM6DSO32_PULL_DOWN_CONNECT, LSM6DSO32_PULL_DOWN_DISC, lsm6dso32_read_reg(), and lsm6dso32_i3c_bus_avb_t::pd_dis_int1.

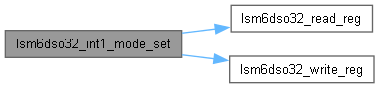

| int32_t lsm6dso32_int1_mode_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_int1_pd_en_t | val | ||

| ) |

Connect/Disconnect INT1 internal pull-down.[set].

| ctx | read / write interface definitions |

| val | change the values of pd_dis_int1 in reg I3C_BUS_AVB |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3052 of file lsm6dso32_reg.c.

References LSM6DSO32_I3C_BUS_AVB, lsm6dso32_read_reg(), lsm6dso32_write_reg(), and lsm6dso32_i3c_bus_avb_t::pd_dis_int1.

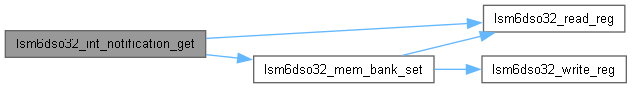

| int32_t lsm6dso32_int_notification_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_lir_t * | val | ||

| ) |

Interrupt notification mode.[get].

| ctx | read / write interface definitions |

| val | Get the values of lir in reg TAP_CFG0 |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3708 of file lsm6dso32_reg.c.

References lsm6dso32_page_rw_t::emb_func_lir, lsm6dso32_tap_cfg0_t::lir, LSM6DSO32_ALL_INT_LATCHED, LSM6DSO32_ALL_INT_PULSED, LSM6DSO32_BASE_LATCHED_EMB_PULSED, LSM6DSO32_BASE_PULSED_EMB_LATCHED, LSM6DSO32_EMBEDDED_FUNC_BANK, lsm6dso32_mem_bank_set(), LSM6DSO32_PAGE_RW, lsm6dso32_read_reg(), LSM6DSO32_TAP_CFG0, and LSM6DSO32_USER_BANK.

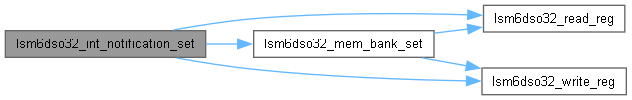

| int32_t lsm6dso32_int_notification_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_lir_t | val | ||

| ) |

Interrupt notification mode.[set].

| ctx | read / write interface definitions |

| val | change the values of lir in reg TAP_CFG0 |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3657 of file lsm6dso32_reg.c.

References lsm6dso32_page_rw_t::emb_func_lir, lsm6dso32_tap_cfg0_t::int_clr_on_read, lsm6dso32_tap_cfg0_t::lir, LSM6DSO32_EMBEDDED_FUNC_BANK, lsm6dso32_mem_bank_set(), LSM6DSO32_PAGE_RW, lsm6dso32_read_reg(), LSM6DSO32_TAP_CFG0, LSM6DSO32_USER_BANK, and lsm6dso32_write_reg().

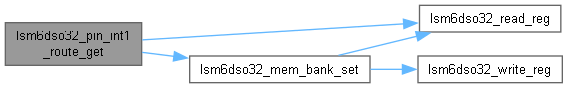

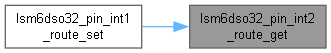

| int32_t lsm6dso32_pin_int1_route_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_pin_int1_route_t * | val | ||

| ) |

Select the signal that need to route on int1 pad.[get].

| ctx | read / write interface definitions |

| val | struct of registers: INT1_CTRL, MD1_CFG, EMB_FUNC_INT1, FSM_INT1_A, FSM_INT1_B |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3251 of file lsm6dso32_reg.c.

References lsm6dso32_pin_int1_route_t::emb_func_int1, lsm6dso32_pin_int1_route_t::fsm_int1_a, lsm6dso32_pin_int1_route_t::fsm_int1_b, lsm6dso32_pin_int1_route_t::int1_ctrl, LSM6DSO32_EMB_FUNC_INT1, LSM6DSO32_EMBEDDED_FUNC_BANK, LSM6DSO32_FSM_INT1_A, LSM6DSO32_FSM_INT1_B, LSM6DSO32_INT1_CTRL, LSM6DSO32_MD1_CFG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_USER_BANK, and lsm6dso32_pin_int1_route_t::md1_cfg.

Referenced by lsm6dso32_pin_int2_route_set().

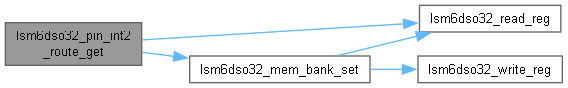

| int32_t lsm6dso32_pin_int1_route_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_pin_int1_route_t * | val | ||

| ) |

Select the signal that need to route on int1 pad.[set].

| ctx | read / write interface definitions |

| val | struct of registers: INT1_CTRL, MD1_CFG, EMB_FUNC_INT1, FSM_INT1_A, FSM_INT1_B |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3113 of file lsm6dso32_reg.c.

References lsm6dso32_int1_ctrl_t::den_drdy_flag, lsm6dso32_pin_int1_route_t::emb_func_int1, lsm6dso32_pin_int1_route_t::fsm_int1_a, lsm6dso32_pin_int1_route_t::fsm_int1_b, lsm6dso32_md1_cfg_t::int1_6d, lsm6dso32_int1_ctrl_t::int1_boot, lsm6dso32_int1_ctrl_t::int1_cnt_bdr, lsm6dso32_pin_int1_route_t::int1_ctrl, lsm6dso32_md1_cfg_t::int1_double_tap, lsm6dso32_int1_ctrl_t::int1_drdy_g, lsm6dso32_int1_ctrl_t::int1_drdy_xl, lsm6dso32_md1_cfg_t::int1_emb_func, lsm6dso32_md1_cfg_t::int1_ff, lsm6dso32_int1_ctrl_t::int1_fifo_full, lsm6dso32_int1_ctrl_t::int1_fifo_ovr, lsm6dso32_int1_ctrl_t::int1_fifo_th, lsm6dso32_fsm_int1_a_t::int1_fsm1, lsm6dso32_fsm_int1_b_t::int1_fsm10, lsm6dso32_fsm_int1_b_t::int1_fsm11, lsm6dso32_fsm_int1_b_t::int1_fsm12, lsm6dso32_fsm_int1_b_t::int1_fsm13, lsm6dso32_fsm_int1_b_t::int1_fsm14, lsm6dso32_fsm_int1_b_t::int1_fsm15, lsm6dso32_fsm_int1_b_t::int1_fsm16, lsm6dso32_fsm_int1_a_t::int1_fsm2, lsm6dso32_fsm_int1_a_t::int1_fsm3, lsm6dso32_fsm_int1_a_t::int1_fsm4, lsm6dso32_fsm_int1_a_t::int1_fsm5, lsm6dso32_fsm_int1_a_t::int1_fsm6, lsm6dso32_fsm_int1_a_t::int1_fsm7, lsm6dso32_fsm_int1_a_t::int1_fsm8, lsm6dso32_fsm_int1_b_t::int1_fsm9, lsm6dso32_emb_func_int1_t::int1_fsm_lc, lsm6dso32_emb_func_int1_t::int1_sig_mot, lsm6dso32_md1_cfg_t::int1_single_tap, lsm6dso32_md1_cfg_t::int1_sleep_change, lsm6dso32_emb_func_int1_t::int1_step_detector, lsm6dso32_emb_func_int1_t::int1_tilt, lsm6dso32_md1_cfg_t::int1_wu, lsm6dso32_md2_cfg_t::int2_6d, lsm6dso32_int2_ctrl_t::int2_cnt_bdr, lsm6dso32_pin_int2_route_t::int2_ctrl, lsm6dso32_md2_cfg_t::int2_double_tap, lsm6dso32_int2_ctrl_t::int2_drdy_g, lsm6dso32_int2_ctrl_t::int2_drdy_temp, lsm6dso32_int2_ctrl_t::int2_drdy_xl, lsm6dso32_md2_cfg_t::int2_ff, lsm6dso32_int2_ctrl_t::int2_fifo_full, lsm6dso32_int2_ctrl_t::int2_fifo_ovr, lsm6dso32_int2_ctrl_t::int2_fifo_th, lsm6dso32_md2_cfg_t::int2_single_tap, lsm6dso32_md2_cfg_t::int2_sleep_change, lsm6dso32_md2_cfg_t::int2_wu, lsm6dso32_tap_cfg2_t::interrupts_enable, LSM6DSO32_EMB_FUNC_INT1, LSM6DSO32_EMBEDDED_FUNC_BANK, LSM6DSO32_FSM_INT1_A, LSM6DSO32_FSM_INT1_B, LSM6DSO32_INT1_CTRL, LSM6DSO32_MD1_CFG, lsm6dso32_mem_bank_set(), lsm6dso32_pin_int2_route_get(), lsm6dso32_read_reg(), LSM6DSO32_TAP_CFG2, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_pin_int1_route_t::md1_cfg, lsm6dso32_pin_int2_route_t::md2_cfg, PROPERTY_DISABLE, and PROPERTY_ENABLE.

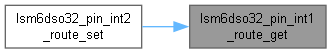

| int32_t lsm6dso32_pin_int2_route_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_pin_int2_route_t * | val | ||

| ) |

Select the signal that need to route on int2 pad.[get].

| ctx | read / write interface definitions |

| val | union of registers INT2_CTRL, MD2_CFG, EMB_FUNC_INT2, FSM_INT2_A, FSM_INT2_B |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3443 of file lsm6dso32_reg.c.

References lsm6dso32_pin_int2_route_t::emb_func_int2, lsm6dso32_pin_int2_route_t::fsm_int2_a, lsm6dso32_pin_int2_route_t::fsm_int2_b, lsm6dso32_pin_int2_route_t::int2_ctrl, LSM6DSO32_EMB_FUNC_INT2, LSM6DSO32_EMBEDDED_FUNC_BANK, LSM6DSO32_FSM_INT2_A, LSM6DSO32_FSM_INT2_B, LSM6DSO32_INT2_CTRL, LSM6DSO32_MD2_CFG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_USER_BANK, and lsm6dso32_pin_int2_route_t::md2_cfg.

Referenced by lsm6dso32_pin_int1_route_set().

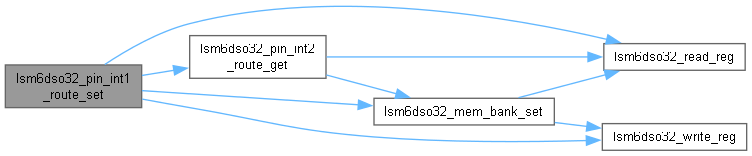

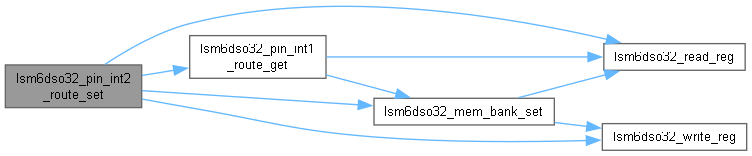

| int32_t lsm6dso32_pin_int2_route_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_pin_int2_route_t * | val | ||

| ) |

Select the signal that need to route on int2 pad.[set].

| ctx | read / write interface definitions |

| val | union of registers INT2_CTRL, MD2_CFG, EMB_FUNC_INT2, FSM_INT2_A, FSM_INT2_B |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3305 of file lsm6dso32_reg.c.

References lsm6dso32_int1_ctrl_t::den_drdy_flag, lsm6dso32_pin_int2_route_t::emb_func_int2, lsm6dso32_pin_int2_route_t::fsm_int2_a, lsm6dso32_pin_int2_route_t::fsm_int2_b, lsm6dso32_md1_cfg_t::int1_6d, lsm6dso32_int1_ctrl_t::int1_boot, lsm6dso32_int1_ctrl_t::int1_cnt_bdr, lsm6dso32_pin_int1_route_t::int1_ctrl, lsm6dso32_md1_cfg_t::int1_double_tap, lsm6dso32_int1_ctrl_t::int1_drdy_g, lsm6dso32_int1_ctrl_t::int1_drdy_xl, lsm6dso32_md1_cfg_t::int1_ff, lsm6dso32_int1_ctrl_t::int1_fifo_full, lsm6dso32_int1_ctrl_t::int1_fifo_ovr, lsm6dso32_int1_ctrl_t::int1_fifo_th, lsm6dso32_md1_cfg_t::int1_single_tap, lsm6dso32_md1_cfg_t::int1_sleep_change, lsm6dso32_md1_cfg_t::int1_wu, lsm6dso32_md2_cfg_t::int2_6d, lsm6dso32_int2_ctrl_t::int2_cnt_bdr, lsm6dso32_pin_int2_route_t::int2_ctrl, lsm6dso32_md2_cfg_t::int2_double_tap, lsm6dso32_int2_ctrl_t::int2_drdy_g, lsm6dso32_int2_ctrl_t::int2_drdy_temp, lsm6dso32_int2_ctrl_t::int2_drdy_xl, lsm6dso32_md2_cfg_t::int2_emb_func, lsm6dso32_md2_cfg_t::int2_ff, lsm6dso32_int2_ctrl_t::int2_fifo_full, lsm6dso32_int2_ctrl_t::int2_fifo_ovr, lsm6dso32_int2_ctrl_t::int2_fifo_th, lsm6dso32_fsm_int2_a_t::int2_fsm1, lsm6dso32_fsm_int2_b_t::int2_fsm10, lsm6dso32_fsm_int2_b_t::int2_fsm11, lsm6dso32_fsm_int2_b_t::int2_fsm12, lsm6dso32_fsm_int2_b_t::int2_fsm13, lsm6dso32_fsm_int2_b_t::int2_fsm14, lsm6dso32_fsm_int2_b_t::int2_fsm15, lsm6dso32_fsm_int2_b_t::int2_fsm16, lsm6dso32_fsm_int2_a_t::int2_fsm2, lsm6dso32_fsm_int2_a_t::int2_fsm3, lsm6dso32_fsm_int2_a_t::int2_fsm4, lsm6dso32_fsm_int2_a_t::int2_fsm5, lsm6dso32_fsm_int2_a_t::int2_fsm6, lsm6dso32_fsm_int2_a_t::int2_fsm7, lsm6dso32_fsm_int2_a_t::int2_fsm8, lsm6dso32_fsm_int2_b_t::int2_fsm9, lsm6dso32_emb_func_int2_t::int2_fsm_lc, lsm6dso32_emb_func_int2_t::int2_sig_mot, lsm6dso32_md2_cfg_t::int2_single_tap, lsm6dso32_md2_cfg_t::int2_sleep_change, lsm6dso32_emb_func_int2_t::int2_step_detector, lsm6dso32_emb_func_int2_t::int2_tilt, lsm6dso32_md2_cfg_t::int2_wu, lsm6dso32_tap_cfg2_t::interrupts_enable, LSM6DSO32_EMB_FUNC_INT2, LSM6DSO32_EMBEDDED_FUNC_BANK, LSM6DSO32_FSM_INT2_A, LSM6DSO32_FSM_INT2_B, LSM6DSO32_INT2_CTRL, LSM6DSO32_MD2_CFG, lsm6dso32_mem_bank_set(), lsm6dso32_pin_int1_route_get(), lsm6dso32_read_reg(), LSM6DSO32_TAP_CFG2, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_pin_int1_route_t::md1_cfg, lsm6dso32_pin_int2_route_t::md2_cfg, PROPERTY_DISABLE, and PROPERTY_ENABLE.

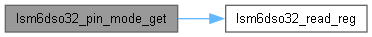

| int32_t lsm6dso32_pin_mode_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_pp_od_t * | val | ||

| ) |

Push-pull/open drain selection on interrupt pads.[get].

| ctx | read / write interface definitions |

| val | Get the values of pp_od in reg CTRL3_C |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3521 of file lsm6dso32_reg.c.

References LSM6DSO32_CTRL3_C, LSM6DSO32_OPEN_DRAIN, LSM6DSO32_PUSH_PULL, lsm6dso32_read_reg(), and lsm6dso32_ctrl3_c_t::pp_od.

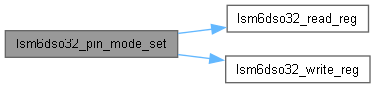

| int32_t lsm6dso32_pin_mode_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_pp_od_t | val | ||

| ) |

Push-pull/open drain selection on interrupt pads.[set].

| ctx | read / write interface definitions |

| val | change the values of pp_od in reg CTRL3_C |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3496 of file lsm6dso32_reg.c.

References LSM6DSO32_CTRL3_C, lsm6dso32_read_reg(), lsm6dso32_write_reg(), and lsm6dso32_ctrl3_c_t::pp_od.

| int32_t lsm6dso32_pin_polarity_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_h_lactive_t * | val | ||

| ) |

Interrupt active-high/low.[get].

| ctx | read / write interface definitions |

| val | Get the values of h_lactive in reg CTRL3_C |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3580 of file lsm6dso32_reg.c.

References lsm6dso32_ctrl3_c_t::h_lactive, LSM6DSO32_ACTIVE_HIGH, LSM6DSO32_ACTIVE_LOW, LSM6DSO32_CTRL3_C, and lsm6dso32_read_reg().

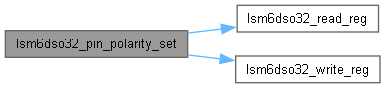

| int32_t lsm6dso32_pin_polarity_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_h_lactive_t | val | ||

| ) |

Interrupt active-high/low.[set].

| ctx | read / write interface definitions |

| val | change the values of h_lactive in reg CTRL3_C |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 3555 of file lsm6dso32_reg.c.

References lsm6dso32_ctrl3_c_t::h_lactive, LSM6DSO32_CTRL3_C, lsm6dso32_read_reg(), and lsm6dso32_write_reg().