|

Da Vinci Firmware 1

Firmware for the DaVinci-M rocket avionics board.

|

|

Da Vinci Firmware 1

Firmware for the DaVinci-M rocket avionics board.

|

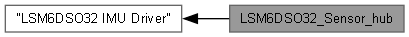

This section groups all the functions that manage the sensor hub. More...

Functions | |

| int32_t | lsm6dso32_sh_read_data_raw_get (stmdev_ctx_t *ctx, lsm6dso32_emb_sh_read_t *val) |

| Sensor hub output registers.[get]. | |

| int32_t | lsm6dso32_sh_slave_connected_set (stmdev_ctx_t *ctx, lsm6dso32_aux_sens_on_t val) |

| Number of external sensors to be read by the sensor hub.[set]. | |

| int32_t | lsm6dso32_sh_slave_connected_get (stmdev_ctx_t *ctx, lsm6dso32_aux_sens_on_t *val) |

| Number of external sensors to be read by the sensor hub.[get]. | |

| int32_t | lsm6dso32_sh_master_set (stmdev_ctx_t *ctx, uint8_t val) |

| Sensor hub I2C master enable.[set]. | |

| int32_t | lsm6dso32_sh_master_get (stmdev_ctx_t *ctx, uint8_t *val) |

| Sensor hub I2C master enable.[get]. | |

| int32_t | lsm6dso32_sh_pin_mode_set (stmdev_ctx_t *ctx, lsm6dso32_shub_pu_en_t val) |

| Master I2C pull-up enable.[set]. | |

| int32_t | lsm6dso32_sh_pin_mode_get (stmdev_ctx_t *ctx, lsm6dso32_shub_pu_en_t *val) |

| Master I2C pull-up enable.[get]. | |

| int32_t | lsm6dso32_sh_pass_through_set (stmdev_ctx_t *ctx, uint8_t val) |

| I2C interface pass-through.[set]. | |

| int32_t | lsm6dso32_sh_pass_through_get (stmdev_ctx_t *ctx, uint8_t *val) |

| I2C interface pass-through.[get]. | |

| int32_t | lsm6dso32_sh_syncro_mode_set (stmdev_ctx_t *ctx, lsm6dso32_start_config_t val) |

| Sensor hub trigger signal selection.[set]. | |

| int32_t | lsm6dso32_sh_syncro_mode_get (stmdev_ctx_t *ctx, lsm6dso32_start_config_t *val) |

| Sensor hub trigger signal selection.[get]. | |

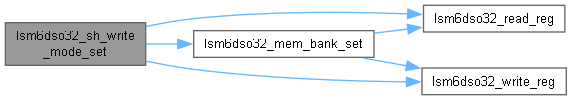

| int32_t | lsm6dso32_sh_write_mode_set (stmdev_ctx_t *ctx, lsm6dso32_write_once_t val) |

| Slave 0 write operation is performed only at the first sensor hub cycle.[set]. | |

| int32_t | lsm6dso32_sh_write_mode_get (stmdev_ctx_t *ctx, lsm6dso32_write_once_t *val) |

| Slave 0 write operation is performed only at the first sensor hub cycle.[get]. | |

| int32_t | lsm6dso32_sh_reset_set (stmdev_ctx_t *ctx) |

| Reset Master logic and output registers.[set]. | |

| int32_t | lsm6dso32_sh_reset_get (stmdev_ctx_t *ctx, uint8_t *val) |

| Reset Master logic and output registers.[get]. | |

| int32_t | lsm6dso32_sh_data_rate_set (stmdev_ctx_t *ctx, lsm6dso32_shub_odr_t val) |

| Rate at which the master communicates.[set]. | |

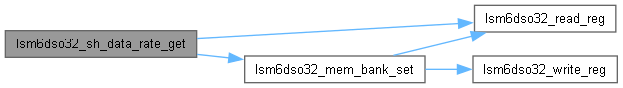

| int32_t | lsm6dso32_sh_data_rate_get (stmdev_ctx_t *ctx, lsm6dso32_shub_odr_t *val) |

| Rate at which the master communicates.[get]. | |

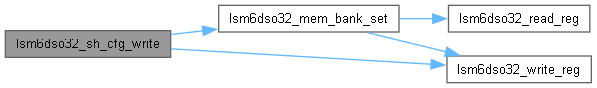

| int32_t | lsm6dso32_sh_cfg_write (stmdev_ctx_t *ctx, lsm6dso32_sh_cfg_write_t *val) |

| Configure slave 0 for perform a write.[set]. | |

| int32_t | lsm6dso32_sh_slv0_cfg_read (stmdev_ctx_t *ctx, lsm6dso32_sh_cfg_read_t *val) |

| Configure slave 0 for perform a read.[set]. | |

| int32_t | lsm6dso32_sh_slv1_cfg_read (stmdev_ctx_t *ctx, lsm6dso32_sh_cfg_read_t *val) |

| Configure slave 0 for perform a write/read.[set]. | |

| int32_t | lsm6dso32_sh_slv2_cfg_read (stmdev_ctx_t *ctx, lsm6dso32_sh_cfg_read_t *val) |

| Configure slave 0 for perform a write/read.[set]. | |

| int32_t | lsm6dso32_sh_slv3_cfg_read (stmdev_ctx_t *ctx, lsm6dso32_sh_cfg_read_t *val) |

| Configure slave 0 for perform a write/read.[set]. | |

| int32_t | lsm6dso32_sh_status_get (stmdev_ctx_t *ctx, lsm6dso32_status_master_t *val) |

| Sensor hub source register.[get]. | |

This section groups all the functions that manage the sensor hub.

| int32_t lsm6dso32_sh_cfg_write | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_sh_cfg_write_t * | val | ||

| ) |

Configure slave 0 for perform a write.[set].

| ctx | read / write interface definitions |

| val | a structure that contain

|

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9551 of file lsm6dso32_reg.c.

References LSM6DSO32_DATAWRITE_SLV0, lsm6dso32_mem_bank_set(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV0_ADD, LSM6DSO32_SLV0_SUBADD, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_slv0_add_t::rw_0, lsm6dso32_slv0_add_t::slave0, lsm6dso32_sh_cfg_write_t::slv0_add, lsm6dso32_sh_cfg_write_t::slv0_data, and lsm6dso32_sh_cfg_write_t::slv0_subadd.

| int32_t lsm6dso32_sh_data_rate_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_shub_odr_t * | val | ||

| ) |

Rate at which the master communicates.[get].

| ctx | read / write interface definitions |

| val | Get the values of shub_odr in reg slv1_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9496 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SH_ODR_104Hz, LSM6DSO32_SH_ODR_13Hz, LSM6DSO32_SH_ODR_26Hz, LSM6DSO32_SH_ODR_52Hz, LSM6DSO32_SLV0_CONFIG, LSM6DSO32_USER_BANK, and lsm6dso32_slv0_config_t::shub_odr.

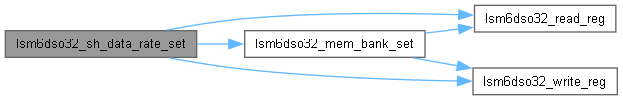

| int32_t lsm6dso32_sh_data_rate_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_shub_odr_t | val | ||

| ) |

Rate at which the master communicates.[set].

| ctx | read / write interface definitions |

| val | change the values of shub_odr in reg slv1_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9461 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV0_CONFIG, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), and lsm6dso32_slv0_config_t::shub_odr.

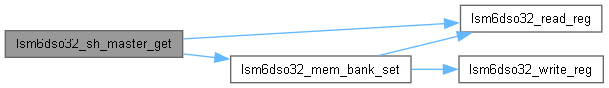

| int32_t lsm6dso32_sh_master_get | ( | stmdev_ctx_t * | ctx, |

| uint8_t * | val | ||

| ) |

Sensor hub I2C master enable.[get].

| ctx | read / write interface definitions |

| val | change the values of master_on in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9043 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, and lsm6dso32_master_config_t::master_on.

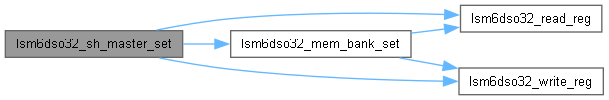

| int32_t lsm6dso32_sh_master_set | ( | stmdev_ctx_t * | ctx, |

| uint8_t | val | ||

| ) |

Sensor hub I2C master enable.[set].

| ctx | read / write interface definitions |

| val | change the values of master_on in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9007 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), and lsm6dso32_master_config_t::master_on.

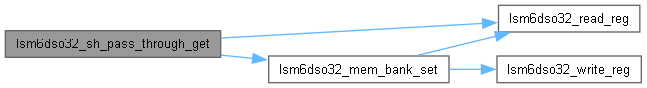

| int32_t lsm6dso32_sh_pass_through_get | ( | stmdev_ctx_t * | ctx, |

| uint8_t * | val | ||

| ) |

I2C interface pass-through.[get].

| ctx | read / write interface definitions |

| val | change the values of pass_through_mode in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9193 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, and lsm6dso32_master_config_t::pass_through_mode.

| int32_t lsm6dso32_sh_pass_through_set | ( | stmdev_ctx_t * | ctx, |

| uint8_t | val | ||

| ) |

I2C interface pass-through.[set].

| ctx | read / write interface definitions |

| val | change the values of pass_through_mode in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9156 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), and lsm6dso32_master_config_t::pass_through_mode.

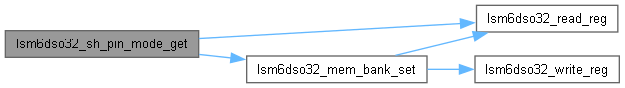

| int32_t lsm6dso32_sh_pin_mode_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_shub_pu_en_t * | val | ||

| ) |

Master I2C pull-up enable.[get].

| ctx | read / write interface definitions |

| val | Get the values of shub_pu_en in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9110 of file lsm6dso32_reg.c.

References LSM6DSO32_EXT_PULL_UP, LSM6DSO32_INTERNAL_PULL_UP, LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, and lsm6dso32_master_config_t::shub_pu_en.

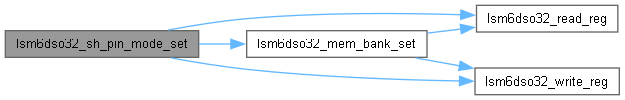

| int32_t lsm6dso32_sh_pin_mode_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_shub_pu_en_t | val | ||

| ) |

Master I2C pull-up enable.[set].

| ctx | read / write interface definitions |

| val | change the values of shub_pu_en in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9073 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), and lsm6dso32_master_config_t::shub_pu_en.

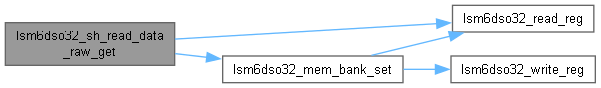

| int32_t lsm6dso32_sh_read_data_raw_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_emb_sh_read_t * | val | ||

| ) |

Sensor hub output registers.[get].

| ctx | read / write interface definitions |

| val | union of registers from SENSOR_HUB_1 to SENSOR_HUB_18 |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 8888 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_1, LSM6DSO32_SENSOR_HUB_BANK, and LSM6DSO32_USER_BANK.

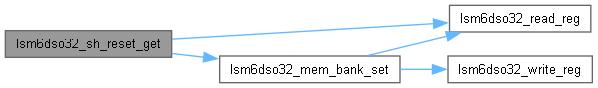

| int32_t lsm6dso32_sh_reset_get | ( | stmdev_ctx_t * | ctx, |

| uint8_t * | val | ||

| ) |

Reset Master logic and output registers.[get].

| ctx | read / write interface definitions |

| val | change the values of rst_master_regs in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9431 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, and lsm6dso32_master_config_t::rst_master_regs.

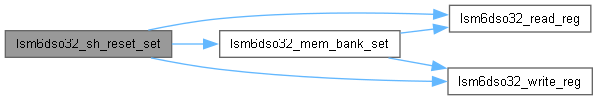

| int32_t lsm6dso32_sh_reset_set | ( | stmdev_ctx_t * | ctx | ) |

Reset Master logic and output registers.[set].

| ctx | read / write interface definitions |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9388 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), PROPERTY_DISABLE, PROPERTY_ENABLE, and lsm6dso32_master_config_t::rst_master_regs.

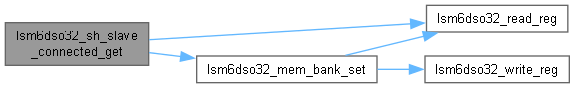

| int32_t lsm6dso32_sh_slave_connected_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_aux_sens_on_t * | val | ||

| ) |

Number of external sensors to be read by the sensor hub.[get].

| ctx | read / write interface definitions |

| val | Get the values of aux_sens_on in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 8954 of file lsm6dso32_reg.c.

References lsm6dso32_master_config_t::aux_sens_on, LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV_0, LSM6DSO32_SLV_0_1, LSM6DSO32_SLV_0_1_2, LSM6DSO32_SLV_0_1_2_3, and LSM6DSO32_USER_BANK.

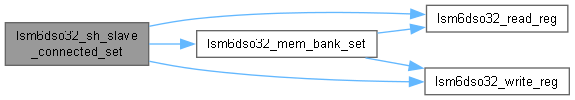

| int32_t lsm6dso32_sh_slave_connected_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_aux_sens_on_t | val | ||

| ) |

Number of external sensors to be read by the sensor hub.[set].

| ctx | read / write interface definitions |

| val | change the values of aux_sens_on in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 8917 of file lsm6dso32_reg.c.

References lsm6dso32_master_config_t::aux_sens_on, LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, and lsm6dso32_write_reg().

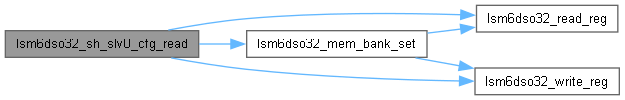

| int32_t lsm6dso32_sh_slv0_cfg_read | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_sh_cfg_read_t * | val | ||

| ) |

Configure slave 0 for perform a read.[set].

| ctx | read / write interface definitions |

| val | Structure that contain

|

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9597 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV0_ADD, LSM6DSO32_SLV0_CONFIG, LSM6DSO32_SLV0_SUBADD, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_slv0_add_t::rw_0, lsm6dso32_slv0_add_t::slave0, lsm6dso32_slv0_config_t::slave0_numop, lsm6dso32_sh_cfg_read_t::slv_add, lsm6dso32_sh_cfg_read_t::slv_len, and lsm6dso32_sh_cfg_read_t::slv_subadd.

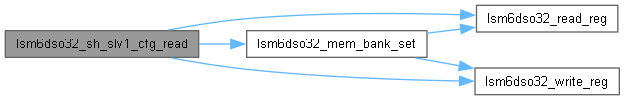

| int32_t lsm6dso32_sh_slv1_cfg_read | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_sh_cfg_read_t * | val | ||

| ) |

Configure slave 0 for perform a write/read.[set].

| ctx | read / write interface definitions |

| val | Structure that contain

|

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9652 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV1_ADD, LSM6DSO32_SLV1_CONFIG, LSM6DSO32_SLV1_SUBADD, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_slv1_add_t::r_1, lsm6dso32_slv1_add_t::slave1_add, lsm6dso32_slv1_config_t::slave1_numop, lsm6dso32_sh_cfg_read_t::slv_add, lsm6dso32_sh_cfg_read_t::slv_len, and lsm6dso32_sh_cfg_read_t::slv_subadd.

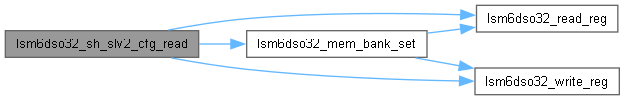

| int32_t lsm6dso32_sh_slv2_cfg_read | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_sh_cfg_read_t * | val | ||

| ) |

Configure slave 0 for perform a write/read.[set].

| ctx | read / write interface definitions |

| val | Structure that contain

|

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9707 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV2_ADD, LSM6DSO32_SLV2_CONFIG, LSM6DSO32_SLV2_SUBADD, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_slv2_add_t::r_2, lsm6dso32_slv2_add_t::slave2_add, lsm6dso32_slv2_config_t::slave2_numop, lsm6dso32_sh_cfg_read_t::slv_add, lsm6dso32_sh_cfg_read_t::slv_len, and lsm6dso32_sh_cfg_read_t::slv_subadd.

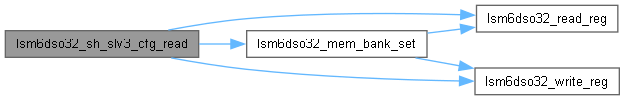

| int32_t lsm6dso32_sh_slv3_cfg_read | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_sh_cfg_read_t * | val | ||

| ) |

Configure slave 0 for perform a write/read.[set].

| ctx | read / write interface definitions |

| val | Structure that contain

|

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9762 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_SLV3_ADD, LSM6DSO32_SLV3_CONFIG, LSM6DSO32_SLV3_SUBADD, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), lsm6dso32_slv3_add_t::r_3, lsm6dso32_slv3_add_t::slave3_add, lsm6dso32_slv3_config_t::slave3_numop, lsm6dso32_sh_cfg_read_t::slv_add, lsm6dso32_sh_cfg_read_t::slv_len, and lsm6dso32_sh_cfg_read_t::slv_subadd.

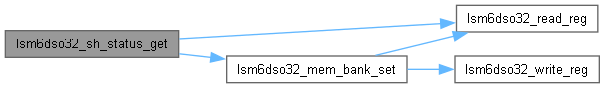

| int32_t lsm6dso32_sh_status_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_status_master_t * | val | ||

| ) |

Sensor hub source register.[get].

| ctx | read / write interface definitions |

| val | union of registers from STATUS_MASTER to |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9814 of file lsm6dso32_reg.c.

References lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_STATUS_MASTER, and LSM6DSO32_USER_BANK.

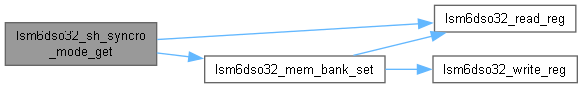

| int32_t lsm6dso32_sh_syncro_mode_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_start_config_t * | val | ||

| ) |

Sensor hub trigger signal selection.[get].

| ctx | read / write interface definitions |

| val | Get the values of start_config in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9260 of file lsm6dso32_reg.c.

References LSM6DSO32_EXT_ON_INT2_PIN, LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, LSM6DSO32_XL_GY_DRDY, and lsm6dso32_master_config_t::start_config.

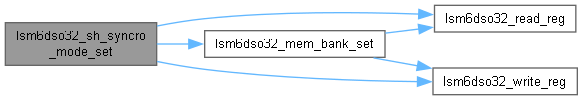

| int32_t lsm6dso32_sh_syncro_mode_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_start_config_t | val | ||

| ) |

Sensor hub trigger signal selection.[set].

| ctx | read / write interface definitions |

| val | change the values of start_config in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9223 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), and lsm6dso32_master_config_t::start_config.

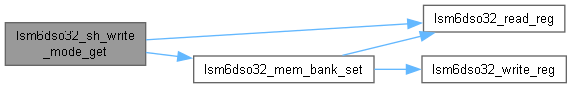

| int32_t lsm6dso32_sh_write_mode_get | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_write_once_t * | val | ||

| ) |

Slave 0 write operation is performed only at the first sensor hub cycle.[get].

| ctx | read / write interface definitions |

| val | Get the values of write_once in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9344 of file lsm6dso32_reg.c.

References LSM6DSO32_EACH_SH_CYCLE, LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), LSM6DSO32_ONLY_FIRST_CYCLE, lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, and lsm6dso32_master_config_t::write_once.

| int32_t lsm6dso32_sh_write_mode_set | ( | stmdev_ctx_t * | ctx, |

| lsm6dso32_write_once_t | val | ||

| ) |

Slave 0 write operation is performed only at the first sensor hub cycle.[set].

| ctx | read / write interface definitions |

| val | change the values of write_once in reg MASTER_CONFIG |

| interface | status (MANDATORY: return 0 -> no Error) |

Definition at line 9306 of file lsm6dso32_reg.c.

References LSM6DSO32_MASTER_CONFIG, lsm6dso32_mem_bank_set(), lsm6dso32_read_reg(), LSM6DSO32_SENSOR_HUB_BANK, LSM6DSO32_USER_BANK, lsm6dso32_write_reg(), and lsm6dso32_master_config_t::write_once.