|

Da Vinci Firmware 1

Firmware for the DaVinci-M rocket avionics board.

|

|

Da Vinci Firmware 1

Firmware for the DaVinci-M rocket avionics board.

|

Functions for checking the driver's internal state and managing the QSPI bus. More...

Functions | |

| HAL_StatusTypeDef | QFlash_WriteEnable () |

| enables writes | |

| HAL_StatusTypeDef | QFlash_WriteDisable () |

| disables writes | |

| HAL_StatusTypeDef | QFlash_WriteSR2 (uint8_t data) |

| writes to register 2 | |

| HAL_StatusTypeDef | QFlash_WriteSR3 (uint8_t data) |

| writes to register 3 | |

| uint8_t | QFlash_IsQSPIAvailable (void) |

| HAL_StatusTypeDef | QFlash_WaitForQSPIAvailable (uint32_t timeout) |

| uint8_t | QFlash_IsDataAvailable (void) |

| HAL_StatusTypeDef | QFlash_WaitForDataAvailable (uint32_t timeout) |

| void | QFlash_DefaultCmd (QSPI_CommandTypeDef *sCommand) |

Functions for checking the driver's internal state and managing the QSPI bus.

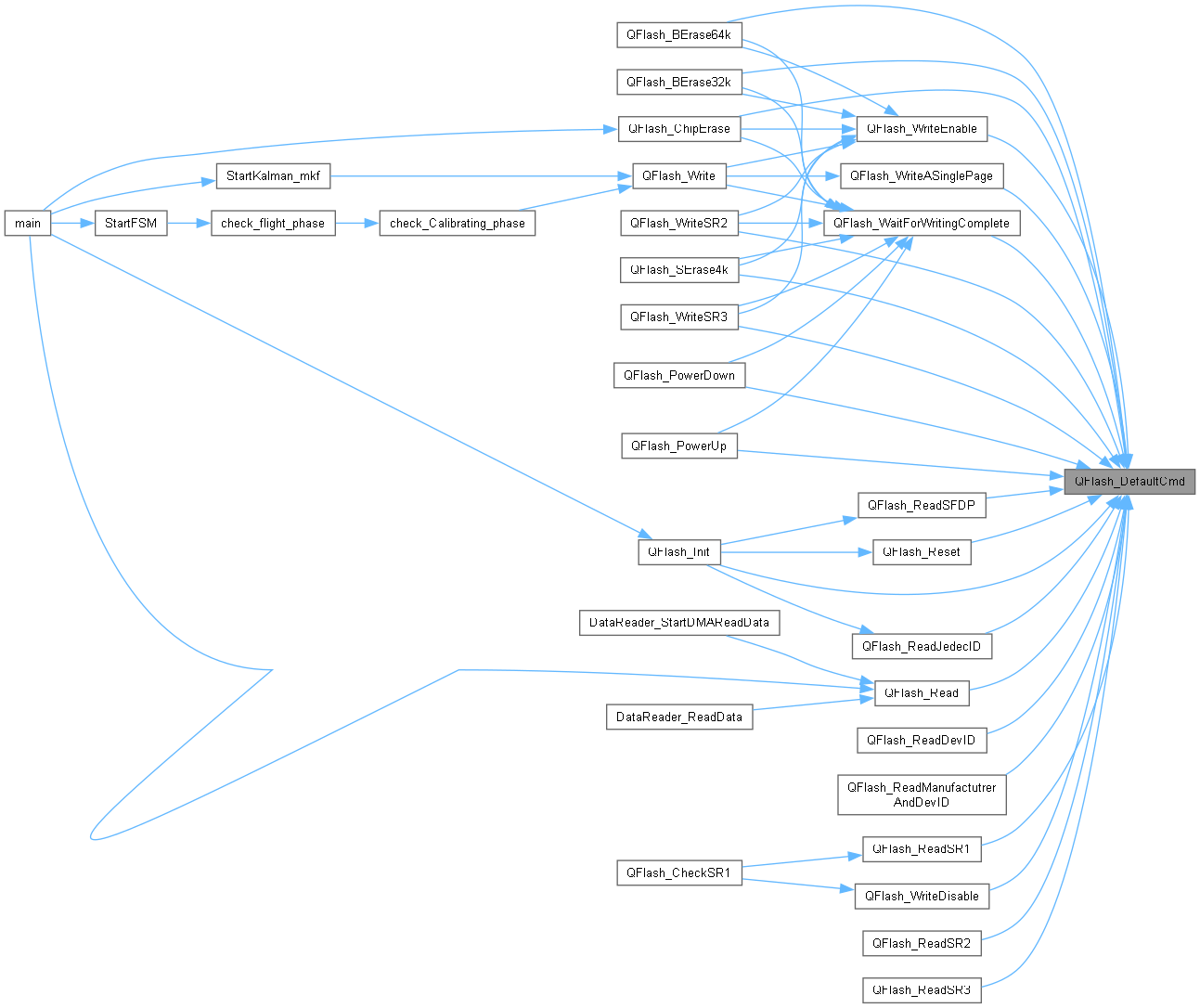

| void QFlash_DefaultCmd | ( | QSPI_CommandTypeDef * | sCommand | ) |

Definition at line 105 of file z_qflash_W25QXXX.c.

References QFLASH_ADDRESS_MODE, QFLASH_ADDRESS_SIZE, QFLASH_ALTERNATE_BYTE_MODE, QFLASH_DATA_MODE, QFLASH_DDR_HOLD_HALF_CYCLE, QFLASH_DDR_MODE, QFLASH_DUMMY_CYCLES, QFLASH_INSTRUCTION_MODE, and QFLASH_SIOO_MODE.

Referenced by QFlash_BErase32k(), QFlash_BErase64k(), QFlash_ChipErase(), QFlash_Init(), QFlash_PowerDown(), QFlash_PowerUp(), QFlash_Read(), QFlash_ReadDevID(), QFlash_ReadJedecID(), QFlash_ReadManufactutrerAndDevID(), QFlash_ReadSFDP(), QFlash_ReadSR1(), QFlash_ReadSR2(), QFlash_ReadSR3(), QFlash_Reset(), QFlash_SErase4k(), QFlash_WaitForWritingComplete(), QFlash_WriteASinglePage(), QFlash_WriteDisable(), QFlash_WriteEnable(), QFlash_WriteSR2(), and QFlash_WriteSR3().

| uint8_t QFlash_IsDataAvailable | ( | void | ) |

| uint8_t QFlash_IsQSPIAvailable | ( | void | ) |

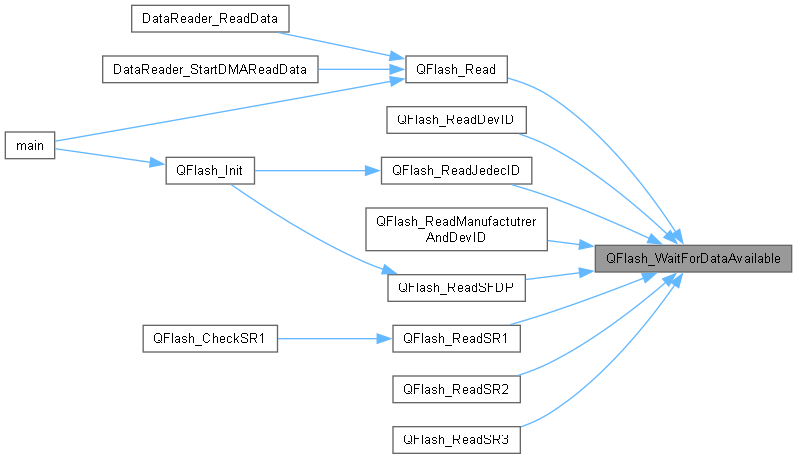

| HAL_StatusTypeDef QFlash_WaitForDataAvailable | ( | uint32_t | timeout | ) |

Definition at line 85 of file z_qflash_W25QXXX.c.

References HAL_ERROR, HAL_OK, and QSpiReadDataAvailable.

Referenced by QFlash_Read(), QFlash_ReadDevID(), QFlash_ReadJedecID(), QFlash_ReadManufactutrerAndDevID(), QFlash_ReadSFDP(), QFlash_ReadSR1(), QFlash_ReadSR2(), and QFlash_ReadSR3().

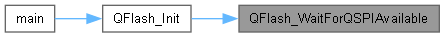

| HAL_StatusTypeDef QFlash_WaitForQSPIAvailable | ( | uint32_t | timeout | ) |

Definition at line 49 of file z_qflash_W25QXXX.c.

References HAL_ERROR, HAL_OK, and QSpiAvailable.

Referenced by QFlash_Init().

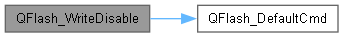

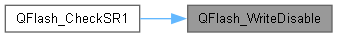

| HAL_StatusTypeDef QFlash_WriteDisable | ( | void | ) |

disables writes

Definition at line 475 of file z_qflash_W25QXXX.c.

References FLASH_QSPI_PORT, HAL_ERROR, HAL_OK, QFLASH_DEF_TIMEOUT, QFlash_DefaultCmd(), QSpiAvailable, and W25_W_DISABLE.

Referenced by QFlash_CheckSR1().

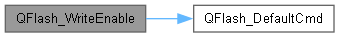

| HAL_StatusTypeDef QFlash_WriteEnable | ( | void | ) |

enables writes

Definition at line 425 of file z_qflash_W25QXXX.c.

References FLASH_QSPI_PORT, HAL_ERROR, HAL_OK, QFLASH_DEF_TIMEOUT, QFlash_DefaultCmd(), QSpiAvailable, and W25_W_ENABLE.

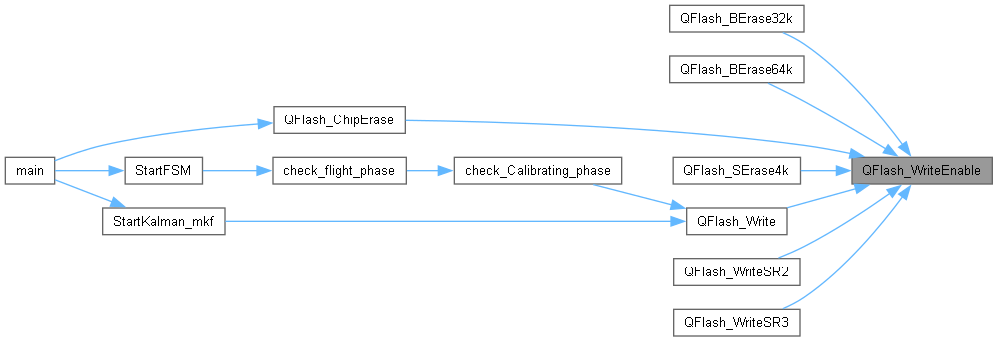

Referenced by QFlash_BErase32k(), QFlash_BErase64k(), QFlash_ChipErase(), QFlash_SErase4k(), QFlash_Write(), QFlash_WriteSR2(), and QFlash_WriteSR3().

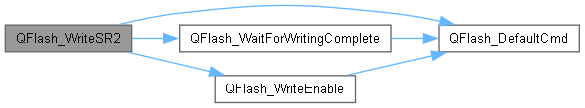

| HAL_StatusTypeDef QFlash_WriteSR2 | ( | uint8_t | data | ) |

writes to register 2

Definition at line 631 of file z_qflash_W25QXXX.c.

References FLASH_QSPI_PORT, HAL_ERROR, HAL_OK, QFLASH_DEF_TIMEOUT, QFlash_DefaultCmd(), QFlash_WaitForWritingComplete(), QFlash_WriteEnable(), QSpiAvailable, QSpiReadDataAvailable, and W25_W_SR2.

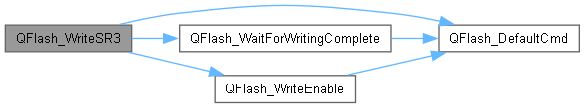

| HAL_StatusTypeDef QFlash_WriteSR3 | ( | uint8_t | data | ) |

writes to register 3

Definition at line 676 of file z_qflash_W25QXXX.c.

References FLASH_QSPI_PORT, HAL_ERROR, HAL_OK, QFLASH_DEF_TIMEOUT, QFlash_DefaultCmd(), QFlash_WaitForWritingComplete(), QFlash_WriteEnable(), QSpiAvailable, QSpiReadDataAvailable, and W25_W_SR3.